ADC的一个重要趋势是转向更高的分辨率。这一趋势影响着一系列的应用,包括工厂自动化、温度检测,以及数据采集。对更高分辨率的需求使设计者们从传统的12位SAR(逐次逼近寄存器)ADC,转向分辨率达24位的Δ-Σ ADC。所有ADC都有某种程度的噪声,包括输入相关噪声以及量化噪声,前者是ADC本身固有的噪声,后者则是在ADC转换时出现的噪声。噪声、ENOB(有效位数)、有效分辨率、无噪声分辨率等指标基本上定义了一款ADC的精度。

因此,了解有关噪声的性能指标要比从SAR转向Δ-Σ ADC更加困难。鉴于当前对更高分辨率的需求,设计者必须更好地了解ADC噪声、ENOB、有效分辨率,以及信噪比。

更高分辨率

过去,一只12位SAR ADC通常就足以测量各种信号与电压输入。如果某个应用需要更精细的测量,设计者可以在ADC前加一个增益级或PGA(可编程增益放大器)。对于16位设计,设计者的选择仍然主要是SARADC,但也包含了某些Δ-Σ ADC。但对16位以上的设计,Δ-Σ ADC正在变得更加适用。SAR ADC现在有18位的极限,而Δ-Σ ADC正将自己的空间扩充到18位、20位和24位。ADC的价格在过去10年有不小的下降,使用也变得更简单,获得了更广泛的理解。

有效分辨率

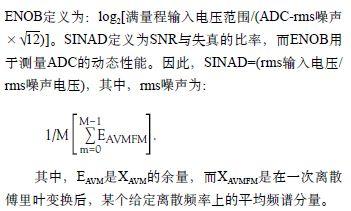

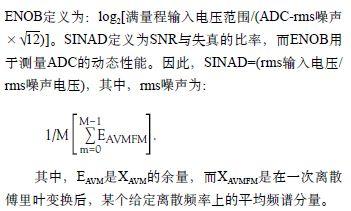

下式定义了有效分辨率的位数: 有效分辨率=log2(满量程输入电压范围/ADC-rms噪声),或更简单地,有效分辨率=log2(VIN/VRMSNOISE)。不要将有效分辨率与ENOB相混淆。测量ENOB的最常用方法是对ADC的一个正弦波输入做快速傅里叶变换分析。IEEE标准1057将

有效分辨率与无噪声分辨率测量的是ADC在基础dc的噪声性能,它不是频谱失真中的因素,包括总谐波失真和无寄生动态范围。一旦知道了ADC的噪声与输入范围,对有效分辨率和无噪声分辨率的计算就变得简单了。

ADC的输入电压范围取决于基准电压。如果ADC包含有一个PGA,则还要把PGA考虑到电压范围内。有些Δ-Σ ADC包括了用于提高小信号增益的PGA。带PGA的最新ADC通常都标示噪声小于100nV rms。虽然这个噪声数字看似比老款ADC有吸引力,但它通常采用的是一个小输入范围,根据基准电压,小的输入范围才能最终放大以适配一个较宽的ADC有效范围。因此,这些ADC的有效分辨率与无噪声分辨率可能弱于那些不带PGA的ADC。

无噪声分辨率

无噪声分辨率采用的是峰峰电压噪声,而不是rms噪声。下式定义了无噪声分辨率的位数:无噪声分辨率=log2(满量程输入电压范围/ADC的峰峰噪声)。无噪声分辨率=log2(VIN/V-p-p噪声)。可以用实验室中的5位半或6位半数字万用表来看待无噪声或无闪烁分辨率。如果显示的最后一位数稳定且不闪烁,则数据输出字就高于系统的噪声水平。以6.6的波峰因数为例,峰峰噪声是rms噪声的6.6倍。因此,有效分辨率要比无噪声分辨率高2.7位。采用相同的噪声与基准值,无噪声分辨率为18.9位。

无噪声计数

无噪声计数是精密系统用于评估ADC性能的另一个指标,尤其是在称重天平等应用中,它可能需要50000个无噪声计数。这个值的计算方法是将无噪声分辨率转换为2N因数的计数。例如,采用式210,一个理想10位ADC有1024个无噪声计数。一个理想的12位 ADC有4096个无噪声计数。同样,采用相同的无噪声分辨率值,该例可得218.9,合489178个无噪声计数。

Δ-ΣADC的过采样

Δ-Σ ADC采用一种过采样结构,这意味着ADC的内部振荡器/时钟频率高于输出数据(或吞吐量)速率。有些Δ-Σ ADC可以改变输出数据的速率,使设计者能够优化采样,在最差噪声情况下获得较高速度,或用更多的过滤和噪声整形(将噪声推入测量区以外的频段)而获得较低速度和更好的噪声性能。很多新的Δ-Σ ADC都以表格形式提供有效分辨率和无噪声分辨率值,从而易于比较权衡。

表1给出了一个ADC的例子,包括双极模式和单极输入模式下的数据速率、噪声、无噪声分辨率,以及有效分辨率。24位的MAX11200 ADC既可以测双极输入,也可以测单极输入。它的工作电压为2.7V~3.6V,基准电压最高可以偏置到电源电压。双极值基于±3.6V的最大输入范围,而单极测量则基于0V~3.6V的输入范围。

设计者可以通过软件,对MAX11200内部振荡器编程,在较低的数据速率设置下为60Hz抑制的2.4576MHz,或在较低数据速率下50Hz抑制的2.048MHz。无论哪种数据速率,ADC噪声都相同。因此,获得的无噪声分辨率与有效分辨率值都是一样的。你可以为一个55Hz陷波滤波器采用外接振荡器,可同时在50Hz与60Hz获得好的抑制效果。

有效的双极分辨率最大为24位,因为输出的数据字长为24位。在三个最低的数据速率设置下,ADC的噪声水平足够的低,如果ADC要在串行接口上输出24位以上数据,则有效分辨率优于24位。除非有数据输出字的限制,否则有效分辨率总是比无噪声分辨率好2.7 位。噪声整形使Δ-Σ ADC能够实现低噪声与高精度。

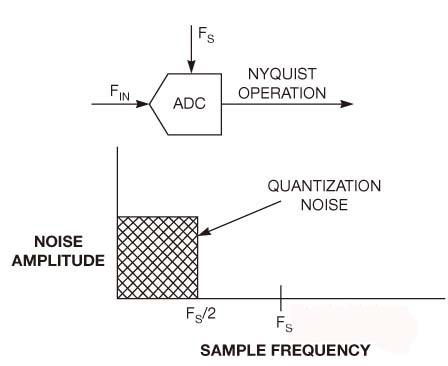

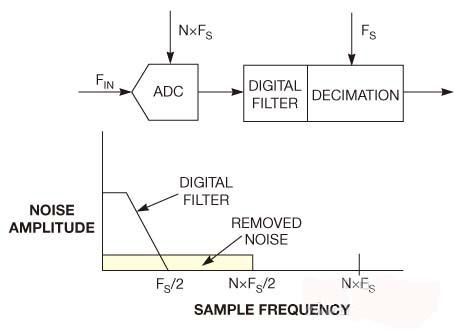

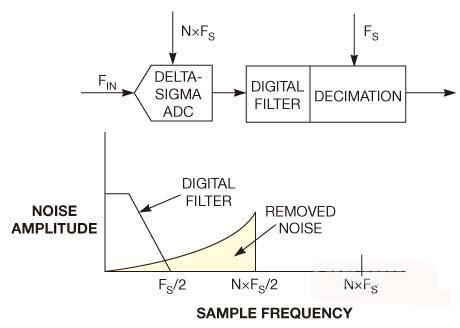

噪声整形、过滤

图1是一个标准ADC的量化噪声,图2详细描述了一只ADC,包括过采样、数字滤波器,以及抽取。大多数采用过采样的ADC核心是Δ-Σ单元。N倍过采样会在较宽的频带上散播噪声,而数字滤波器可消除大部分噪声。图3详解了一个Δ-Σ调制器,它在图2的相同块中增加了噪声整形。将噪声推至不对称的较高频率,可使噪声位于最低频带。这种技术使Δ-Σ ADC制造商能够实现优于1μV rms的噪声值。

图1,一个标准ADC的噪声性能弱于Δ-Σ ADC器件。

图2,一个采用N倍过采样、数字滤波器和抽取的ADC改进了噪声性能。

图3,在一个采用N倍过采样、噪声整形、数字滤波器、抽取的ADC中,ADC输入频带内的噪声(黄色)大大降低。

有了过采样能力和固有的低噪声,Δ-Σ ADC成为需要较高分辨率的系统的最佳设计选择。随着设计者必须处理的信号越来越小,选择正确ADC的关键就变为要准确地理解ADC噪声、有效分辨率、ENOB,以及无噪声分辨率。