特性:

VCO频率范围:1750Mhz~2250Mhz,6对LVPECL(最大输出频率1.6Ghz)输出和4对LVDS输出(800Mhz)。

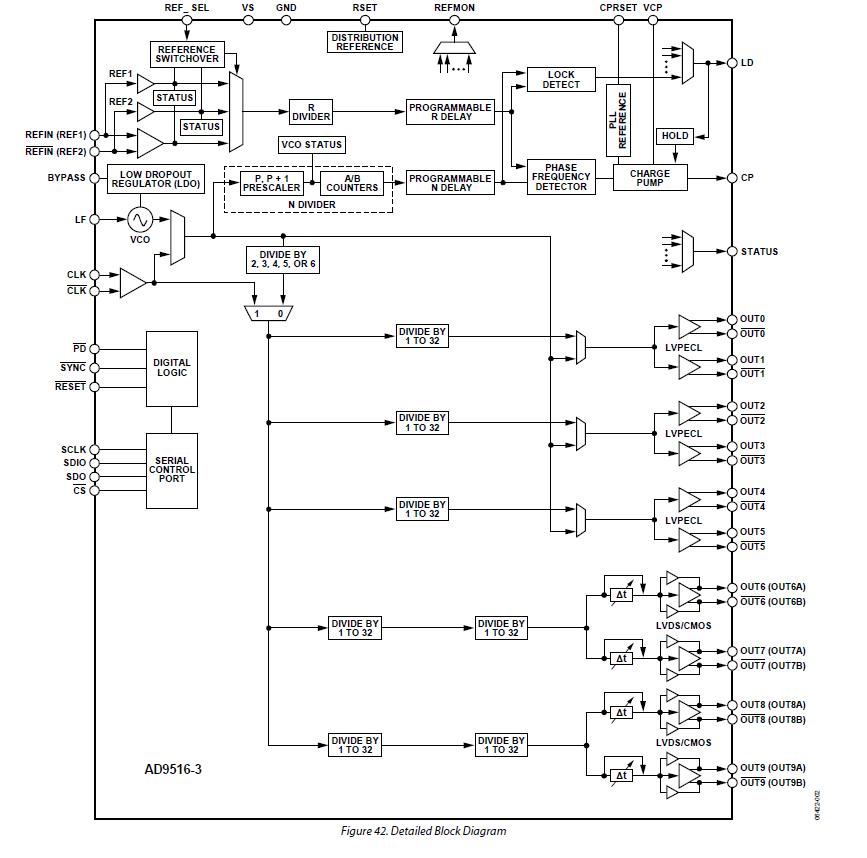

内部结构:

如下图所示,常用引脚说明:

REF1:参考输入1,

REF2:参考输入2,

REF_SEL:选择是参考输入1或者参考输入2

LF:环路滤波器输出,使用内部VCO时使用

CLK:外部VCO输入

SYNC:同步输入,低有效,如果不同步,直接拉高。

REFMON:参考的输出,详细看datasheet

STATUS:状态输出,详细看datasheet

LD: PLL状态指示,详细看datasheet。

需要用的工具

AD9516_17_18 Evaluation Software.exe

AD9516_17_18EvalSetup1.1.0.zip

使用步骤

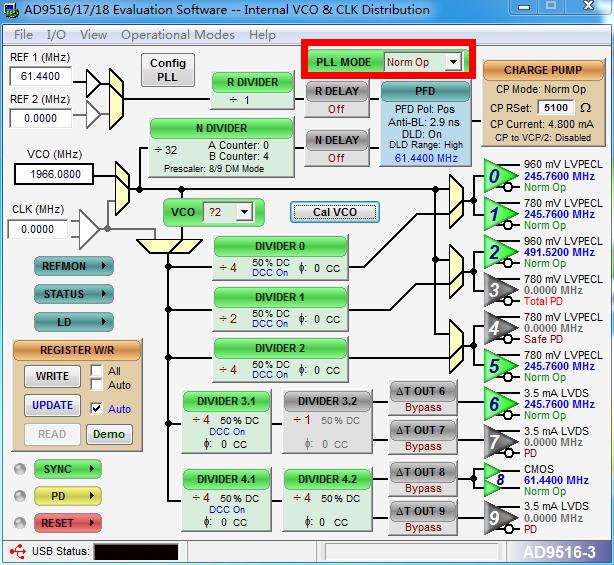

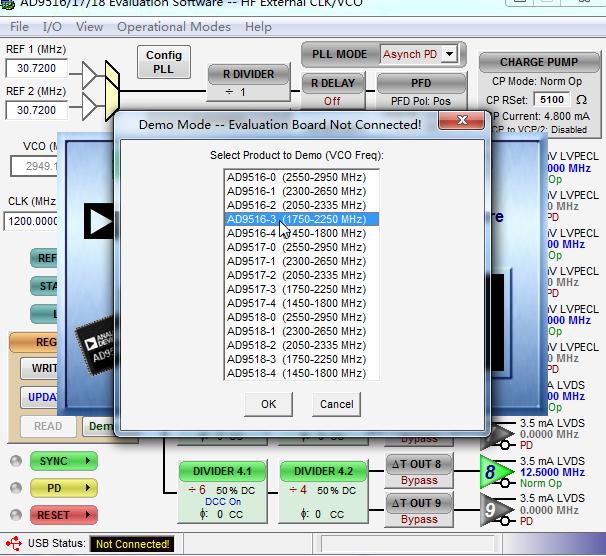

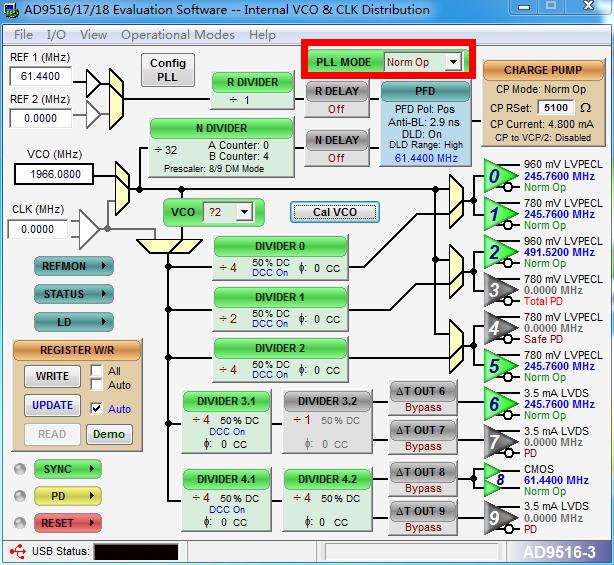

软件界面如下:

输入你的参考时钟,我以我的自己的例子来讲解哈。

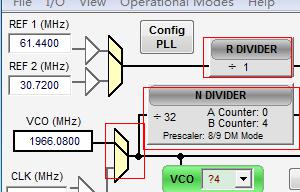

1我使用了REF1=61.44Mhz,那么在REF1中输入61.44,并选择为输入(点击黄色块)。

2配置N分频和R分频,这个要稍微计算下咯。以R=1为例。VCO的频率范围为1750Mhz~2250Mhz,则N的范围为1750/61.44~2250/61.44即28.48~36.6,则可选的值为29~36

考虑到我的输出,选择N=32,同时选择内部VCO作为N分频的输入。

3根据需要配置输出,并选择PLL MODE 为NormOp

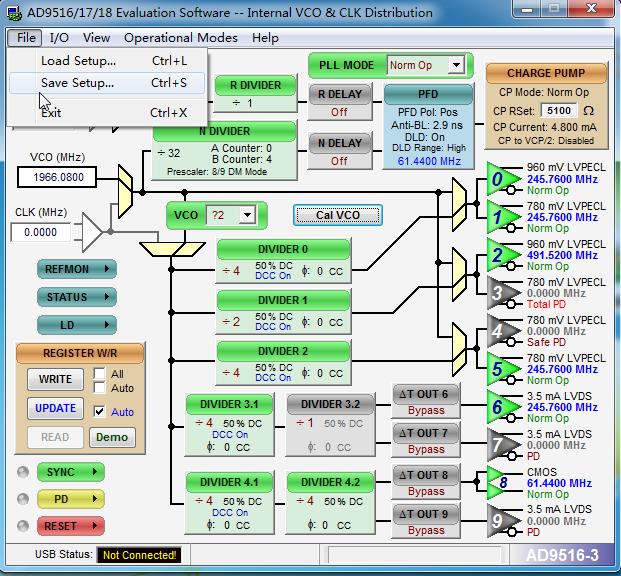

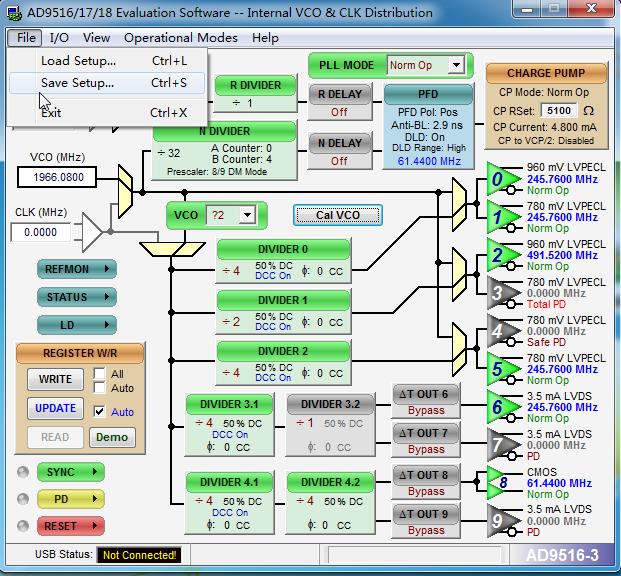

4导出配置文档,导出的文档格式为stp格式,可以直接用记事本打开。

4导出配置文档,导出的文档格式为stp格式,可以直接用记事本打开。

5查看配置文档,找出变化了寄存器值(也可以不找出,将全部寄存器值写进去也可以)。

配置注意事项

在配置完成后注意校准VCO。

示例如下:

5查看配置文档,找出变化了寄存器值(也可以不找出,将全部寄存器值写进去也可以)。

配置注意事项

在配置完成后注意校准VCO。

示例如下:

——回复可见——

module Control_AD9516(

input CLK,

input Reset_n,

input Send_Busy,

// input AD9516_LD,

output reg[23:0]Dataout,

output reg AD9516_SYNC,

output reg Start_Sig

);

/***************************************/

parameter R0_R =24'h00003C; //soft reset

parameter R0 =24'h000018;

parameter R10 =24'h00107C; //1100 power on

parameter R11 =24'h001101; // R=4

parameter R14 =24'h001404; // B=16 N=16*8=128

parameter R16 =24'h001604; // mode 8 / 9

parameter R17 =24'h001700; // status = N divider output

parameter R18 =24'h001807; //initial

parameter R18_R =24'h001806; //Reset VCO calibration

parameter R1B =24'h001BA0; //open VCO frequency monitor and Ref1 frequency monitor

parameter R1C =24'h001C02; //select ref1 power on

parameter RF0 =24'h00F008; //out0 output V=780mV 1000

parameter RF1 =24'h00F108; //out1 outupt V=780mV

parameter RF2 =24'h00F208; //out2 outupt V=780mV

parameter RF3 =24'h00F30B; //out3 Total power down 1011

parameter RF4 =24'h00F40B; //out4 Total power down 1011

parameter RF5 =24'h00F508; //out5 output V=780mV

parameter R140 =24'h014042; //out6 output I=3.5MA

parameter R141 =24'h014143; //out7 power down

parameter R142 =24'h01425a; //out8 COMS output

parameter R143 =24'h014343; //out9 power down

parameter R190 =24'h019011; // out0 & out 1 divider 4 get 245.76Mhz

parameter R191 =24'h019100;

parameter R193 =24'h019300; // out 3 divider 2 get 491.52Mhz

parameter R196 =24'h019611; // out 5 divider 4 get 245.76Mhz

parameter R199 =24'h019911; // out 6 divider 4 get 245.76Mhz

parameter R19B =24'h019B00;

parameter R19C =24'h019C20;

parameter R19E =24'h019E11; //out 8 divider 4*4 get 61.44Mhz

parameter R1A0 =24'h01A011;

parameter R1E0 =24'h01E000; //VCO divider 2 get 983.04Mhz

parameter R1E1 =24'h01E102; //Select VCO as source CLK

parameter R232 =24'h023201; //updata all Reg

/***************************************/

reg [5:0]count;

reg flag;

//reg [2:0]count_sync;

/***************************************/

always @ (posedge CLK or negedge Reset_n)

if(!Reset_n)begin

Start_Sig <= 1'b0;

count <= 6'd0;

flag <= 1'b0;

Dataout <= 24'd0;

AD9516_SYNC <= 1'b1;

// count_sync <= 3'd0;

end

else if (count < (6'd35))begin

AD9516_SYNC <= 1'b1;

if((!Send_Busy) && (!flag))begin

flag <= 1'b1;

Start_Sig <= 1'b1;

case (count)

0:begin Dataout <= R0_R; end //soft reset

1:begin Dataout <= R0;end //clear reset

//PLL config

2:begin Dataout <= R10; end //PPL power on

3:begin Dataout <= R11; end //VCO =1966.08Mhz; N =128;

4:begin Dataout <= R14; end //REF1 =61.44Mhz; R=4;

5:begin Dataout <= R16; end

6:begin Dataout <= R17; end

7:begin Dataout <= R1B; end

8:begin Dataout <= R1C; end

//output Config

9:begin Dataout <= RF0; end //out 0

10:begin Dataout <= RF1;end //out 1

11:begin Dataout <= RF2;end //out 2

12:begin Dataout <= RF3;end //out 3

13:begin Dataout <= RF4;end //out 4

14:begin Dataout <= RF5;end //out 5

15:begin Dataout <= R140;end //out 6

16:begin Dataout <= R141;end //out 7

17:begin Dataout <= R142;end //out 8

18:begin Dataout <= R143;end //out 9

//output divider

19:begin Dataout <= R190;end

20:begin Dataout <= R191;end

21:begin Dataout <= R193;end

22:begin Dataout <= R196;end

23:begin Dataout <= R199;end

24:begin Dataout <= R19B;end

25:begin Dataout <= R19C;end

26:begin Dataout <= R19E;end

27:begin Dataout <= R1A0;end

//VCO Config

28:begin Dataout <= R1E0;end

29:begin Dataout <= R1E1;end

30:begin Dataout <= R232;end

//VCO calibraion

31:begin Dataout <= R18_R;end

32:begin Dataout <= R232; end

33:begin Dataout <= R18; end

34:begin Dataout <= R232; end

endcase

end

if (flag)begin

flag <= 1'b0;

Start_Sig <=1'b0;

count <= count + 1'b1;

end

end

endmodule

遇见的问题

1、 输出频率有偏差,但频率稳定(PLL锁定了),检查参考频率,参考频率的极小偏差都有可能导致输出频率偏差

2、 输出为直流,检查SYNC电平,应该为高。

举报

举报

举报

举报