ADF4002特性 相位检测 频率合成

400Mhz 带宽

104Mhz 频率相位检测

调试说明:

利用ADI PLL Int-N

调试说明:

利用ADI PLL Int-N ,选择ADF4002,根据需求得到想要的值即可。

配置顺序如下所示。

,选择ADF4002,根据需求得到想要的值即可。

配置顺序如下所示。

ADI_Int-N_Setup_v7_3_1.zip

ADI PLL Int-N 使用说明

软件界面如下所示:

ADI_Int-N_Setup_v7_3_1.zip

ADI PLL Int-N 使用说明

软件界面如下所示: 首先选择ADF4002,如下图所示:

首先选择ADF4002,如下图所示:

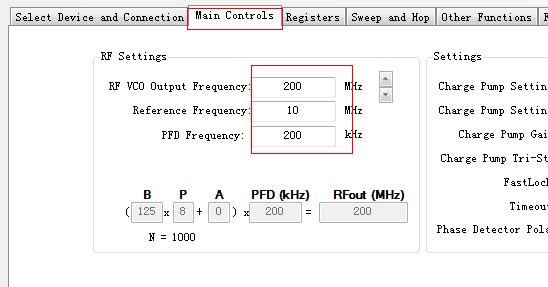

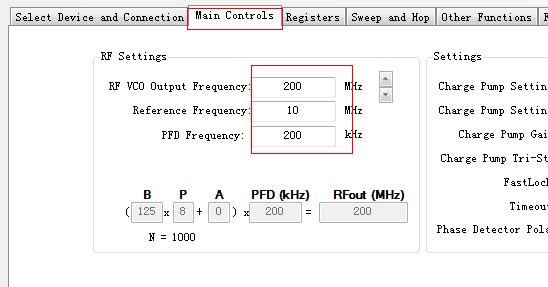

然后进入Main Controls界面,输入你的频率和你要的频率即可得到寄存器的值。

然后进入Main Controls界面,输入你的频率和你要的频率即可得到寄存器的值。

。

示例代码 Verilog

。

示例代码 Verilog

case (count)

57:if(!CLK_AD9516)begin

count <= 0;

SEND_Start <= 1'b0;

Send_Busy <= 1'b0;

end

/********************************************/

//write data

//send data and pull down CSB

0:if(!CLK_AD9516)begin

AD9516_SCLK <=1'b0;

AD9516_CSB <= 1'b0;

count <= count+1'b1;

Temp_Out <=Data[23-(count / 2'd2)];

end

// clk

1,3,5,7,9,11,13,15,17,19,21,23,25,27,29,31,33,35,37,39,41,43,45:

if(CLK_AD9516)begin AD9516_SCLK <=1'b1;count <= count+1'b1;end

//data

2,4,6,8,10,12,14,16,18,20,22,24,26,28,30,32,34,36,38,40,42,44,46:

if(!CLK_AD9516)begin

AD9516_SCLK <= 1'b0;

count <= count+1'b1;

Temp_Out <=Data[23-(count / 2'd2)];

end

//clk

47:if(CLK_AD9516)begin

AD9516_SCLK <= 1'b1;

count <= count+1'b1;

end

//send data over

48:if(!CLK_AD9516) begin

AD9516_SCLK <= 1'b0;

Temp_Out <= 1'b0;

count <= count+1'b1;

end

,选择ADF4002,根据需求得到想要的值即可。

,选择ADF4002,根据需求得到想要的值即可。

举报

举报

举报

举报