随着低功耗的手持式设备越来越多,混合有 5 V、3.3 V、2.5 V 和 1.8 V 器件的印刷

电路板也越来越多普遍,这使得 JTAG 链的设计成为一项极具挑战性的任务。设计者师不仅必须确定 JTAG 链的工作电压,同时还必须确定这些使用不同电压的器件的安放顺序。本文比较了多种设计多电压 JTAG 链的方法,并提供了一些有关执行强大的无故障设计的提示和技巧。

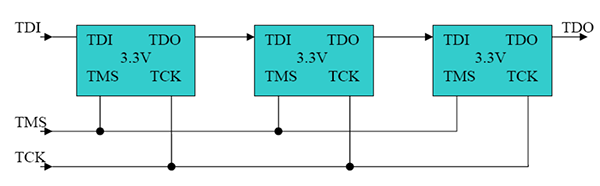

菊花链,或通过其 JTAG 端口连接多个 DSP、

FPGA、CPLD 和其他逻辑器件,使得它们可以通过单个 JTAG 连接器进行控制。菊花链常用于具有多个 JTAG 器件的电路板,它可以将 TDI 和 TDO 引脚连接在一起以形成一个串行路径。链的输入是第一 个器件的 TDI;链的输出是最后一个器件的 TDO。所有器件的 TRST、TCK 和 TMS 引脚均并行连接。通过提供一些可安装或移除(具体取决于所需的目标器件)的跳线,菊花链允许链中的一个或多个器件被绕过以进行调试目的。理论上,通过菊花链连接的器件数量可以是无限的,但是如果菊花链中的器件数量超过八个,就会经常出现时序问题和间歇性的崩溃,特别是时钟速率较高时,更是如此。

当一个链中有超过四个左右的器件时,为了满足 JTAG 时序要求,应在 TCK 和 TMS 上安装缓冲器以保持信号的完整性,并且每个缓冲器驱动的器件数量不应超过四个。例如,一个具有六个器件的菊花链需要两个用于 TCK 的缓冲器和两个用于 TMS 的缓冲器。驱动器必须高速运行(低传播延迟),并有足够的力量来驱动四个或更多个器件。

硬件工程师可能需要用菊花链连接多个具有不同 I/O 电压的器件。通过一个链连接所有器件可能并非是一个最佳的解决方案,因此设计师应该考虑对菊花链进行分区,从而满足专有调试工具的要求。可能需要电平转换器来应对多种电压水平,并且必须保持信号的完整性。设计和测试的复杂性日益增加,并且需要具有 IEEE 1149.1 专业知识来集成和测试系统。下面介绍了两种实现多电压 JTAG 链的方法。

适用于每个电压系列的单独 JTAG 链

这种方法推荐用于多个器件具有相同 I/O 电压的场合,它把所有具有相同 JTAG I/O 电压的器件放在一个链中,从而为每个电压使用单独的链。每个链支持同一类别的所有器件,消除了其他器件无法正常工作的机率,并且在其他厂商必须连接 JTAG 链时可以减少混淆。图 1 显示了具有相同 I/O 电压器件的 JTAG 链。在此情况下,不需要使用电压转换器 (VT)。

图 1:具有相同 I/O 电压的器件的 JTAG 链

多电压 JTAG 链

有时, 把所有 JTAG 器件放在单个链中会更好。当每个电压系列中的器件数量不足以创建单独的 JTAG 链时,推荐采用此方法。要在一个 JTAG 链中成功连接两个具有不同电压的器件,必须满足以下要求:

驱动器的 VOHmin(最低高输出电压)必须大于接收器的 VIHmin(最低输入高电压)。

驱动器的 VOLmax(最高输出低电压)必须小于接收器的 VILmax(最高输入低电压)。

来自驱动器的输出电压不得超过接收器的 I/O 电压容差。

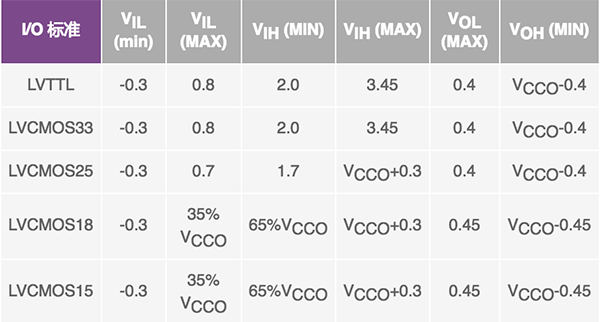

表 1 显示了不同电压标准的常见最低和最高电压。如需了解更具体的数据,设计师应参考零件的数据手册。

表 1:典型 I/O 标准及其相关的最低和最高电压

多电压 JTAG 链的设计指南

多电压 JTAG 链的设计指南

把电压最高的器件放在链的开头,接下来是电压第二高的器件,依次类推,最后放置电压最低的器件。按照从最高电压到最低电压的顺序放置 JTAG 信号,允许一个器件的 TDO 输出上的逻辑高电平可由下一个器件的输入正确解译。

确认每个器件可以承受来自上一个器件的最高电压。例如,如果第一个器件的电压为 3.3 V,下一个器件的电压为 1.8 V,请确保 1.8 V 器件的输入可以至少承受 3.6 V 的电压。

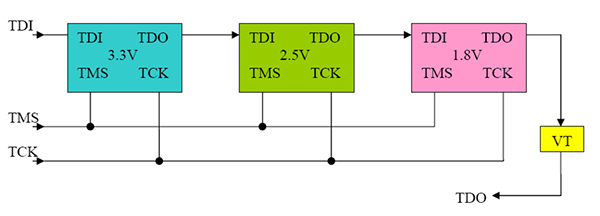

确认来自最低电压器件的 TDO 可由

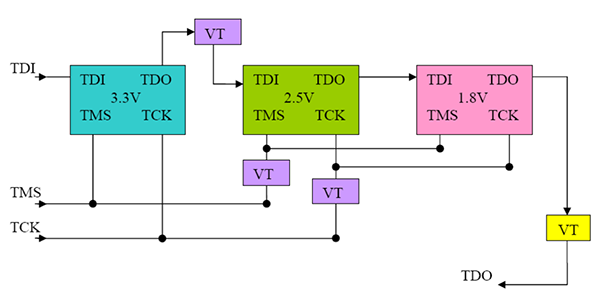

仿真器正确解译。在本示例中,请确保 1.8 V 器件的 VOHmin 大于 3.3 V 器件的 VIHmin。否则,应使用高速电压转换器将 TDO 转换成仿真器的正确电压。VT 不应该寄存(时钟)信号,因为这将延迟一个时钟的信号,导致 JTAG 链失败。模拟装置的 ADG3304 双向逻辑电平转换器包含四个双向通道,可用于多电压数字系统应用中。图 2 显示了具有 3.3 V、2.5 V 和 1.8 V I/O 电压的器件,其中最低电压器件的 I/O 可以承受上一器件的更高电压。对 TDO 采用了电压转换器 (VT),以将电压从 1.8 V 提升到 3.3 V。

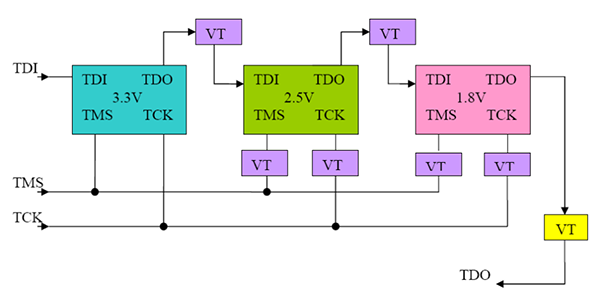

图 2:JTAG 链中的三个器件具有不同的 I/O 电压当具有较低电压的器件不能承受上一器件的高电压时,应在所有 JTAG 信号上使用高速电压转换器。除了 TDO 外,应将仿真器用作所有电压转换器的输入。不要串联电压转换器,因为这会增加传播延迟。图 3 说明了较低电压器件不能承受更高电压 I/O 的情况,因此每个信号都需要使用电压转换器。

图 3:三个具有不同 I/O 电压的器件采用了 JTAG 信号电压转换器如果仅有一个器件不能承受来自上一个器件的 I/O 电压,则只需在该器件上使用电压转换器。例如,JTAG 链中具有 3.3 V、2.5 V 和 1.8 V 的 I/O 电压,1.8 V 器件具有可以承受 2.5 V 的 I/O,因此 2.5 V 信号可由 1.8 V 器件使用。在图 4 中,2.5 V 器件不具有可以承受 3.3 V 的 I/O,但 1.8 V 器件可以承受 2.5 V,因此只需对 2.5 V 器件使用电压转换器。

图 4:三个具有不同 I/O 电压的器件。1.8 V 器件具有与 2.5 V 电压兼容的 I/O

使用肖特基二极管取代电压转换器:

如果大约 0.4 V 的压降足以将电压从较高的水平调整到较低的水平,则可以使用具有快速恢复时间的肖特基二极管来代替电压转换器。ON Semiconductor 提供的 1SS383T1G 肖特基二极管具有 0.48 V 的正向电压降和 25 pF 的容性负载。在此应用中,也可使用 Diodes Inc. 提供的 SD103ATW,它包含三个完全隔离的肖特基二极管,具有大约 0.3 V 的正向电压降和 50 pF 的容性负载。

如需了解 JTAG 信号的完整详情,请参阅 “IEEE 标准测试访问端口和边界扫描结构”。