![]()

![]()

数据速率 HEVC

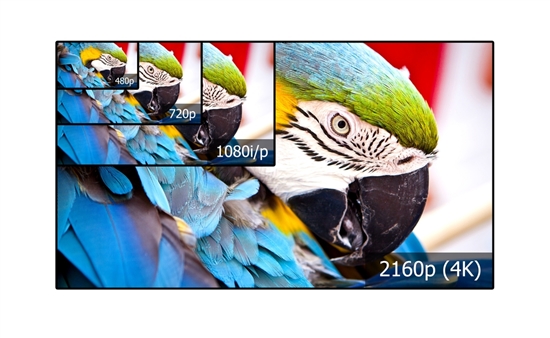

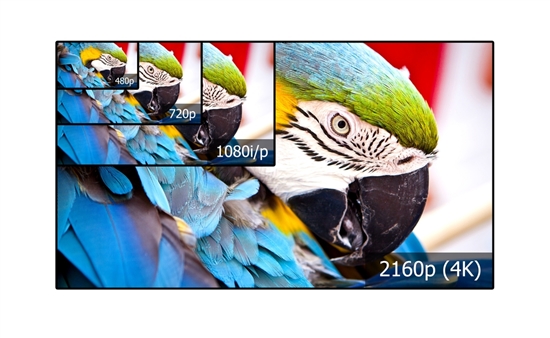

这是因为有希望实现高效视频编码或HEVC。也被称为H.265,它是H.264/MPEG-4高级视频编码 (AVC) 标准的后续标准。HEVC提供同样的视频质量,但是将数据带宽减少50%。这使得HEVC不但非常适合于传输标清 (SD) 内容,而且适用于更高分辨率和帧速率高清 (HD) 和超高清 (UltraHD) 视频,其中包括速率为60fps的4K视频。

HEVC是一个高效,但是处理密集的视频标准,此标准编码复杂度是H.264的5倍至10倍,解码复杂度是H.264的2倍。这意味着需要巨大的处理能力,并且必须在针对商用和消费类系统的可行功率包络幅度内实现。ti TMS320C6678 8个内核DSP能够以仅仅10W的功率在很长的距离上传送320GMAC和160 GFLOP,而又不会增加功率预算,从而缓解了性能问题。

另外一点需要注意的是,诸如针对H.265而定义的标准通常规定了解码过程,但是不规定编码是如何实现的。这就需要编码系统设计人员去考虑性能/延迟/功率之间的均衡关系,并生成一个相容比特流。此外,与H.264一样,HEVC标准会在未来几年有所发展,其中包括针对特定问题域和/或市场细分的改进与提升。因此,在选择编码器解决方案和相关处理平台时需要考虑的一个重要因素就是它实现解决方案的灵活性。在这个方面,DSP经优化的编码看上去在通用处理器和ASIC/FPGA等实线连接的解决方案之间提供一个让人能够接受的媒介。

为了显示出在TI处理器上的轻松实现,TI已经在近期发布了一款针对HEVC的TI设计。这款免费设计表现出,如何用一个或多个C6678 DSP来实时执行一个高功效、软件H.265/HEVC解决方案;这个解决方案可在分辨率、帧速率和系统配置范围内缩放。单通道HEVC 720p30实时编码器和单通道HEVC 1080p60实时解码器的一个专门使用情况也包括在内。此设计包括针对TI TMDSEVM6678电路板的电路原理图、设计文件、和物料清单,以及免费软件,其中包括TI的C66x经优化HEVC编码器和解码器,TI的多内核软件开发套件 (MCSDK) 框架和其它软件包。与现有的H.264x编码器相比,TI特性丰富的HEVC编码器将比特率节省了大约40%,而同时又支持多种分辨率、系统配置和帧速率。

在与HEVC TI设计一同提供的设计指南中查看所支持的不同配置、性能基准测试和电路板级功率估算值。我们也十分想听一听你对于HEVC的看法,谈一谈这项技术的使用,以及在面对不断增长的视频数据流量时它所遇到的困难与阻碍。

更多回帖