如何使电力

电子装置的效率更高、体积更小、重量更轻、成本更低、更加可靠耐用,长期以来一直是各设计、生产者不断努力和追求的方向。解决这一问题最为有效的途径,是采用系统集成的方法使多种电力电子器件组合成为标准化模块,并封装为一体,构成集成电力电子模块。

集成电力电子模块既不是某种特殊的

半导体器件,也不是一种无源

元件。它是按照最优化

电路拓扑和系统结构的原则而设计出的包含多种器件的集成组件或模块。除了具备有功率半导体器件外,还包含驱动电路、控制电路、传感器、保护电路、辅助

电源及无源元件。

集成与封装技术作为电力电子集成模块的一个重点研究方向,主要研究模块的集成和封装工艺。目前已有越来越多的学者认识到,能否真正将集成模块的概念付诸实现,在很大程度上取决于集成和封装的工艺技术。

1传统封装结构与互连方式存在的主要问题

1 封装技术是研究电力电子集成模块的核心问题

电力电子集成的基本思路可以分成单片集成和多芯片混合集成两种。由于高压、大电流的主电路和其它低压、小电流电路的集成工艺完全不同,还有高压隔离和传热的问题,因此,目前仅在数十瓦的功率范围内实现了单片集成。电力电子集成封装技术的主要发展方向为混合集成,即将不同工艺的硅片封装在一个模块中。

混合集成中,首先面临的是集成模块的封装问题。与普通IC不同,集成模块的封装更主要是使模块具备更大的电流承载能力,更高的功率密度和更高效的散热能力。另一方面,对集成模块封装技术的研究是研究与之相关的各类问题的基础和平台。主电路、控制电路等的优化设计与实现,模块内的电磁兼容问题、寄生参数等的分析,控制、传感技术以及高效的散热方式等等,几乎所有相关研究都必须在此基础上展开。

具体到封装技术,又涉及模块的封装结构、模块内芯片与基板的互连方式、各类封装材料(导热、填充、绝缘)的选取、制备的工艺流程等许多问题。由于集成模块无论在功能和结构上都与传统IC或功率器件存在巨大差异,因此新型的模块封装结构和与之相适应的引线工艺又是封装技术中重点并且首先需要研究的问题。

1.2传统封装结构与互连方式存在的主要问题

传统的电力电子器件或模块,虽然外形封装样式多种多样,但其采用的封装结构形式以平面型为主。然而对于电力电子集成模块,由于隔离和散热等问题,难以将功率芯片、控制芯片等多个不同工艺的硅片采用平面型结构安装在同一块底板上。

引线工艺主要解决裸芯片的各电极如何与基板互连的问题。传统电力电子器件采用的互连工艺主要有键合与压接两种方式。前者适用于电流容量为50~600A的器件,由于工艺成熟、成本低,应用较为广泛;后者适用于电流超过500~3000A的器件。然而,这两种互连方式由于其固有的缺陷,均不能简单照搬到电力电子集成模块上。其中压接方式的缺陷主要体现在对管芯、压块、底板等零件平整度要求很高,否则不仅使模块的接触热阻增大,而且会损伤芯片,严重时使芯片碎裂;要保证施加合适的压力,压力过大,会损伤芯片;压力过小,不仅使正向峰值压降、热阻增大,而且会使这两个参数不稳定;由于热应力会使弹簧片等紧固件发生较大的塑性形变,使加在芯片上的压力发生变化,造成正向峰值压降和热阻不稳定;工艺设备复杂,成本,高,壳内零件较多易引起芯片沾污。

引线键合技术本身存在诸多技术缺陷表现在:多根引线并联会产生邻近效应,导致同一硅片的键合线之间或同一模块内的不同硅片的键合线之间电流分布不均;由于高频大电流通过互相平行的引线产生电磁场,由此形成的电磁力容易造成引线老化;引线键合工艺的寄生

电感很大,会给器件带来较高的开关过电压,形成开关应力;引线本身很细,又普遍采用平面封装结构,传热性能不够好;引线和硅片作为不同的材料,二者热膨胀系数的差异会产生热应力等等。

因此,低寄生参数、高性能、能有效传热、高可靠性的新型电力电子集成模块的封装结构和互连方式成为电力电子模块集成工艺中研究的主要问题。

2新型封装结构与互连方式的研究现状

为了获得高性能的电力电子集成模块,以混合封装技术为基础的多芯片模块 (Mul

ti-Chip Module--MCM)封装是目前国际上该领域研究的主流方向。随着三维混合封装技术的发展,目前的MCM已不只局限于将几块芯片平面安装在一块衬底上,而是采用埋置、有源基板或叠层技术,在三维空间内将多个不同工艺的芯片互连形成完整功能的模块。 将MCM技术用于电力电子集成封装的研究,核心内容是研究具有高载流能力、低漏感、高可靠性、三维传热能力和低成本、便于制造的互连和封装工艺,从而解决寄生参数、散热和可靠性问题。目前,国际上已提出多种技术方案,根据其互连方式大体可以划分为两类:以焊接技术为基础的互连工艺和以沉积金属膜(薄膜或厚膜)为基础的互连工艺。

2.1 焊接技术为基础的互连工艺

以焊接技术为基础的互连工艺普遍采用叠层型三维封装结构,即把多个裸芯片或多芯片模块(MCM)沿Z轴层层叠装、互连,组成三维封装结构。叠层型三维封装的优点是工艺相对简单,成本相对较低,关键是解决各层间的垂直互连问题。根据集成功率模块的特殊性,主要利用焊接工艺将焊料凸点、金属柱等焊接在芯片的电极引出端,并与任一基板或芯片互连。目前的技术方案包括焊料凸点互连(Solder Ball Interconnect)和金属柱互连平行板结构(Metal Posts Interconnected Parallel Plate Structures--MPIPPS)等。

(1)焊料凸点互连(Solder Ball Interconnect)

该技术利用焊料凸点代替引线构成芯片电极的引出端,并常与倒装芯片技术(Flip-Chip Technology)结合,以进一步缩短引线间距。倒装芯片技术是在芯片的输入/输出端利用平面工艺制成焊料凸点焊球,将芯片面朝下,直接贴装在基片上,利用回流焊工艺使芯片焊球和基板焊盘之间形成焊点,实现芯片与基板的电、热、机械连接。焊料凸点互连的优点在于省略了芯片和基板之间的引线,起电连接作用的焊点路径短、接触面积大、寄生电感/电容小,封装密度高。

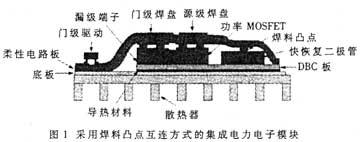

图1所示为采用焊料凸点互连的集成电力电子模块的结构示意图。在模块的结构设计中采用了柔性电路板,并与倒装芯片技术相结合,使功率芯片借助焊料凸点倒扣在柔性电路板上,而芯片的另一面经DBC板与散热器固定。应用焊料凸点互连方式的集成功率模块的缺点在于:由于芯片的热膨胀系数和底板的热膨胀系数存在热膨胀失配,因此在芯片服役(工作时发热,不工作时冷却)中,热膨胀失配严重。在热循环加载下,焊点内产生很大的周期性塑性形变,萌生裂缝并扩展,使焊点很快疲劳失效。

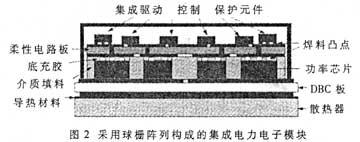

文献[3]对焊料凸点互连技术进行了改进。一方面通过应用底充胶(underfill)技术,即在芯片和基板间隙填充聚合物,机械耦合了芯片与基板的热膨胀失配,提高焊点寿命;另一方面将焊料凸点互连技术与球栅阵列封装(Ball Grid Array--BGA)相结合,进一步减小了集成模块的电气寄生参数,提高了散热性能。图2为采用球栅阵列工艺技术构成的集成电力电子模块。除采用类似的三维叠层封装结构外,由于是在硅片表面以阵列方式制出球形触点作为引脚,不仅使封装尺寸更为缩小,达到与芯片尺寸封装(Chip Scale Package --CSP)接近的封装密度,而且解决了确保获得好的芯片(know goodie--KGD)的问题,使功率芯片可以象普通芯片一样进行测试老化筛选,成品率更有保证。

(2)金属柱互连平行板结构(Metal Posts Interconnected Parallel Plate Structures--MPIPP)

图3所示为金属柱互连平行板结构的封装示意图。在硅片的正反两面上下各有一层互相平行的陶瓷覆铜板(Direct Bond Copper--DBC)。DBC板上都预先刻蚀有相应的电路。硅片的底面直接焊接在DBC板上,而硅片正面的电极是通过直接键合的金属柱引出,与上DBC板构成电气连接,即借助金属柱完成了硅片之间及上下DBC板之间的互连。上DBC板作为一双面基板,安装驱动、保护等元件构成控制电路,与下DBC板的功率电路共同组成具备独立完整功能的集成电力电子模块。

(3)其他互连方式

类似的以焊接技术为基础的互连方式还包括仙童公司的球栅阵列MOSFET,摩托罗拉公司的多芯片机械电子功率封装(Multichip Mechatronics Power Package),CPES的凹陷阵列互连(Dimple Array Interconnect-DAI)等。其中DAI技术是在铜带上制作类似球栅阵列的凹陷阵列,将凹陷的凸起作为芯片的互连引线。与凸焊点相比,凹陷阵列的凸起高度可以做的更高,使互连更加可靠,在铜带上制作凹陷的工艺相对也较为简单。

2.2沉积金属膜为基础的互连工艺

以沉积金属膜为基础的互连工艺多采用埋置型三维封装结构,即在各类基板或介质中埋置裸芯片,顶层再贴装表贴元件及芯片来实现三维封装结构。典型结构如图4所示。其特点是蒸镀或溅射的金属膜不仅与芯片的电极相连,而且可以构成电路图形,并连至其他电路。

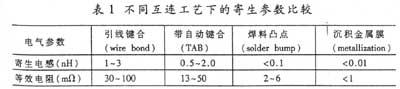

其最大优点是能大大减少焊点,缩短引线间距,进而减小寄生参数。表1所示为几种互连工艺的寄生参数比较。可以看出,不论寄生电感还是等效电阻,沉积金属膜为基础的互连工艺都是最低的。另外,这种互连工艺采用的埋置型三维封装结构能够增大芯片的有效散热面积,热量耗散可以沿模块的各个方向流动,有利于进一步提高集成模块的功率密度。

以沉积金属膜为基础的互连工艺有:薄膜覆盖技术和嵌入式封装等。

(1)薄膜覆盖技术(Thin Film Power Overlay Technology)

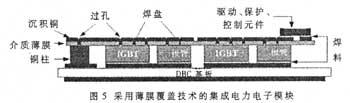

图5为采用薄膜覆盖技术构成的功率模块的结构示意。首先在功率芯片上涂覆聚酰亚胺介质薄膜。之后利用激光在薄膜上烧灼过孔,与下面芯片的电极相通。再用溅射法使过孔金属化,然后涂覆金属层,并图形化。最上层表贴驱动、控制、保护元件。薄膜覆盖技术的优点是能够制作耐压等级高、电流大、高效散热的集成功率模块。

(2)嵌入式封装(Embedded Power Technology)

图6为嵌入式封装的结构示意图。首先在陶瓷框架上刻蚀出空洞,功率芯片被埋设在陶瓷框架的空洞内,之后,在其上部利用丝网漏印、光刻等技术分别涂覆介质薄膜以及金属膜并使之图形化,最后,集成模块的驱动、控制、保护元件以表贴或膜式元件的形式粘附在最上层。嵌入式封装结构的最大优点是可以大为缩小模块的体积,继而提高模块的功率密度。和焊接技术为基础的互连工艺相比,芯片电极引出线的距离更短,相应的寄生参数也更小。

针对电力电子集成模块的新型集成与封装技术的研究是电力电子集成领域的研究重点。传统的平板型、螺栓型等封装结构以及引线键合、压接等互连方式由于存在各种缺陷,不适用于电力电子集成模块。以MCM为基础的三维封装技术具有组装密度高、寄生参数小、功耗低等优点,成为集成模块的发展方向。其中,以焊接技术为基础的互连方法工艺相对简单,成本相对较低;以沉积金属膜为基础的互连方法结构更紧凑,寄生参数更小,更利于三维散热,但工艺较为复杂。