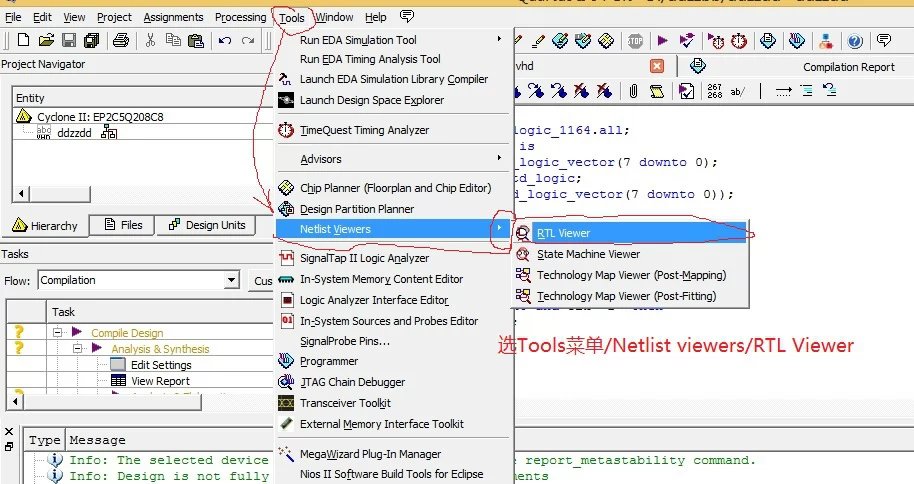

| 1.--VHDL中,wait until clk='1' 可代clk'event and clk='1'做上升沿, --wait until clk='0' 可代clk'event and clk='1'做下降沿。用法如下: --74hc161功能芯片的VHDL程序: Library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity d_ff is Port(clk,cr,ld:in std_logic; d:in std_logic_vector(3 downto 0); q:out std_logic_vector(3 downto 0)); end; architecture dd of d_ff is signal s,ss:std_logic_vector(3 downto 0); begin process begin wait until clk='1'; --这句意思是等待到clk等于1时完成下面语句 if ld='0' then s<=d; else s<=s+1 ; end if; if cr='0' then s<="0000"; end if; end process; q<=s; end dd; 2--子程序也是很多编程语言中常用的程序模块,VHDL子程序用法如下: 1)---------------子程序function的用法-------- Library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity full_adder is Port(a,b,cin:in std_logic; sum,co:out std_logic); end; architecture add of full_adder is Function sam1(x,y:std_logic)return std_logic is --子程序1,sam1为程序名 begin --x,y为子程序变量,冒号后面是变量类型 return (x xor y); --子程序返回值 end sam1; --结束子程序1 function sam2(x,y:std_logic)return std_logic is --子程序2 begin return (x and y); end sam2; --结束子程序1 signal s1,co1,s2,co2,ss:std_logic; begin process(a,b,cin) begin s1<=sam1(a,b); --调用子程序1 co1<=sam2(a,b); --调用子程序2 s2<=sam1(s1,cin); co2<=sam2(s1,cin); end process; sum<=s2; co<=co1 or co2; end dd; 2)---------------子程序Procedure的用法--------- Library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity d_ff is Port(a,b,cin:in std_logic; sum,co:out std_logic); end; architecture dd of d_ff is --------------------------------------- Procedure sam(x,y:in std_logic; z,w: out std_logic) is --这个子程序用法变量必须设置方向 begin z:=x xor y; --赋值必须采用变量Veriable格式:= w:=x and y; end sam; begin process(a,b,cin) variable s1,s2,co1,co2:std_logic;--运行过程中需要的话,必须使用局部变量,在Process后设置。 begin sam(a,b,s1,co1); sam(cin,s1,s2,co2); sum<=s2; co<=co1 or co2; end process; end dd; 3.程序块Block的编辑与使用 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY ppp IS PORT(a,b,c,D,clk: IN STD_LOGIC; y,s,co,Q: OUT STD_LOGIC); END ppp; ARCHITECTURE Behave OF ppp IS signal tmp1,tmp2,tmp3,tmp4,s1,c1,s2,c2:STD_LOGIC; BEGIN g1:BLOCK BEGIN process(clk) begin tmp1 <= a and b; tmp2<= a and (b or (not c)); tmp3<=c xor(not( a and b)); if clk'event and clk='1' then y<=tmp3 or (tmp2 and tmp1); end if; end process; END BLOCK g1; g2:block begin s1<= a xor b; c1<= a and b; s<=s1 xor c; c2<=s1 and c; co<=c1 or c2; end block g2; G3:block begin process(D,clk) begin if clk'event and clk='1' then Q<=D; end if; end process; end block g3; END Behave; 4. for i in 0 to 7 loop 语句 ------------------------------------------------------ library ieee; use ieee.std_logic_1164.all; entity fulladder is Port(D:in std_logic_vector(7 downto 0); clk:in std_logic; Q:out std_logic_vector(7 downto 0)); end; architecture add of fulladder is begin process(D,clk) begin for i in 0 to 7 loop if clk'event and clk='1' then q(i)<=d(i); end if; end loop; end process; end; ------------------------------------------------------------------- 5.quartusII11.0程序综合通过后要生成图像按下图操作  |

更多回帖