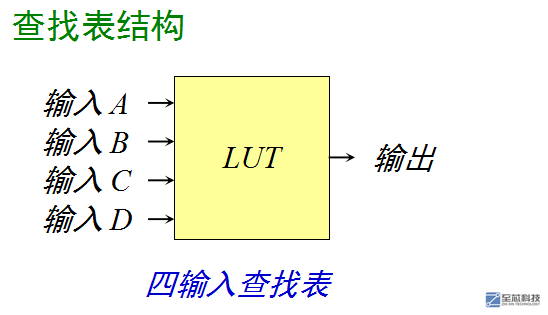

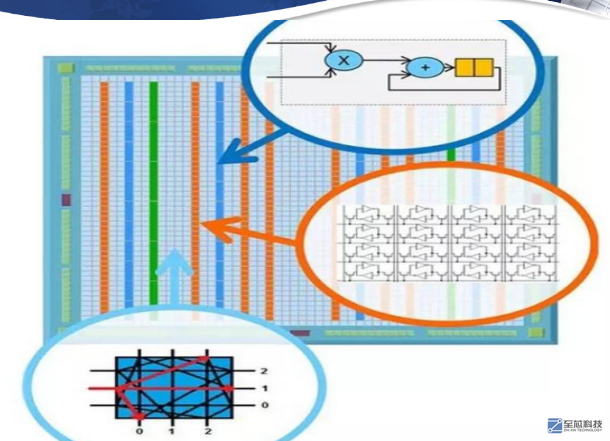

| 大家好,又到了每日学习的时候了。自1985年问世以来,FPGA这种可编程逻辑器件凭借在性能、上市时间、成本、稳定性和长期维护方面的优势,在通信、医疗、工控和安防等领域占有一席之地。特别是近两年,随着云计算、高性能计算和人工智能的繁荣,拥有先天优势的FPGA更是得到了前所未有的关注。近几年随着国家开始大力发展实业,国内集成电路行业发展越来越好,随之由于用户对性能的要求越来越高,FPGA的可编程、高速度、低功耗、较低的二次开发成本的优越特性,带动了FPGA行业的发展,有很多同学们开始自学FPGA。 首先,先来了解一下FPGA,FPGA:Field-Programmable Gate Array,中文名字:现场可编程门阵列。FPGA由六部分组成:可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核。英特尔首席执行官科再奇曾这样描述:“你可以把FPGA想象成一堆gate,能够随时编程。FPGA可以用作多个领域的加速器,例如在加密的同时进行面部搜索,并能在微秒内重新编程。其成本远低于大规模单个定制部件,并具有更高的灵活性。” FPGA是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。 下图为四输入查找表结构。   下图为FPGA架构(举例 Intel AlteraCyclone II EP2C20)  下图为FPGA的结构 下图为FPGA的结构 关于FPGA概念以及结构等等的介绍就到这里,如果大家还想要详细了解,可以自己去查阅资料。接下来,咱们就来聊聊初学FPGA时需要注意哪些知识点或者小细节,希望对大家的学习有所帮助。 *************************************************************************************************************************** ***区别一下软硬件几种类型*** *************************************************************************************************************************** ***通用应用软件*** a. 软件汇编语言(Assembly Language)是面向机器的程序设计语言。 b. 主要关心逻辑和抽象,关心代码量大了之后复杂度可控。硬件资源较多,硬件性能差别较大,不需要针对特定资源设计。 c. 逻辑分层较多,来源于抽象的性能损耗可以接受。甚至于现在很多主流语言构建在虚拟机和解释器上。 d. 非实时。 e. 不需要了解底层硬件原理。 *************************************************************************************************************************** ***嵌入式软件(面向硬件编程)*** a. 时序可控。大部分场景要求实时,因为要满足硬件时序。非抢占的任务调度和中断队列都会引入定时的偏差。 b. 资源开销可控。因为嵌入式硬件环境大多只有有限的 RAM 和 Flash 资源。 c. 针对特定硬件环境设计。 d. 所有代码上的抽象和优化都必须是零损耗或者损耗可控(可以参考 rust 语言)。比较典型的是 GC 会引入严重的时序和资源不可控,所以系统语言很少使用。 *************************************************************************************************************************** ***数字逻辑电路设计(硬件描述性语言)*** a. 数字电路设计不是编程,是设计的时候先有电路,再用语言描述出来。 b. 时序要求更严,需要考虑建立时间和保持时间,及随之而来的亚稳态。 c. Coding style 会明显的影响电路性能。逻辑都一样,但是 DFF 的位置不一样,就可能导致时序不满足。 d. 并行化。执行顺序不再是 CPU 的顺序执行,而是多个并行的流水线。比如快速傅立叶 FFT。比如路由器的 CAM,单次动作完成整表查表。 *************************************************************************************************************************** 1. FPGA学习时使用的 VHDL 和 verilog HDL 不是编程语言,而是一种可综合的硬件描述语言,我们在描述的时候一定要明白所要设计的是一个怎样的电路。 2. 当今社会做开发用的 Verilog HDL 语言偏多,Verilog HDL 支持两种进程 initial 和 always 进程,前者只能用在TB(TestBench)中,后者才是可综合的。 3. 阻塞与非阻塞指都是相对于进程本身而言的,简单来讲,阻塞用在描述组合逻辑电路,而非阻塞用于时序逻辑电路。 4. 使用进程模块的电路类型: 组合电路-----对组合逻辑中使用的所有输入敏感 例子: always@(a or b or c) 时序电路-----仅对时钟和控制信号敏感 例子: always @(posedge clk or negedge rst_n) always既可以描述组合逻辑,也可以描述时序逻辑。 5. 可以用case语句完成多路选择器的功能,但是列举的情况一定要考虑全,否则会产生Latch。 6. verilog中有两类子程序: 函数和任务 函数-----根据输入返回一个值 -----产生组合逻辑 -----用在表达式中:assign mult_out=mult(ina,inb); -----函数是组合逻辑,不能含有任何延时,事件,或者时序控制声明,至少有一个输入变量 总是返回一个变量 -----可以调用函数,但是不能调用任务。 任务-----可以是组合或者寄存器 -----以声明的形式调用任务:stm_out(nxt,first,sel,filter); -----与其他编程语言中的任务相似 -----与函数不同任务不需要传递参数,而函数要传递参数 -----可以调用任务和函数。 ----- 可以含有任何延时,事件,或者时序控制声明 -----返回零个或者多个数值 可综合的verilog语法子集是指用硬件可以实现的语法。力求用最简单的语言实现最复杂的硬件电路。 7. 硬件都有相应的输入输出的接口,或者是输入或者是输出,或者是输入输出。 8. reg 型是指时序逻辑里面的一个寄存数据(寄存机类型),wire 是组合逻辑里面的一条连线(线型)。 9. define 定义了一个参数,在整个工程里面都是有效地使用。 parameter 定义的一个参数只在当前文件里面进行使用。 10. 各种逻辑操作符,移位操作符,算术操作符大多是可综合的。 11. assign一般是只针对于组合逻辑,而always语句既可以用于组合逻辑又可以用于时序逻辑,always模块的敏感表,如果是电平,则为组合逻辑,如果是沿信号posedge或者negedge 则为时序逻辑。 12. begin----end和C语言里面的{}是类似的。 13. for 语句-----循环因为综合出来的结果可能比较浪费资源,所以就一般用的比较少,但是在一些特定的设计中可以起到事半功倍的效果。 14. Total logic element 总共消耗的逻辑单元。 15. 行为级仿真可以理解为功能仿真(前仿真);布局布线后仿真可以理解为时序仿真(后仿真)。 16. 时序逻辑中时钟和复位信号是必须的。 17. 注意wire赋值的一个问题如下: wire[2:0] key_an=key_rst_r&(~key_rst) 其相当于如下的一个赋值语句 wire[2:0] key_an; assign key_an=key_rst_r&(~key_rst); 其实现的效果是一样的。 此种方法为: 脉冲边沿检测法。 18. 实际工作中,除了描述仿真测试激励(Testbench)时使用for循环语句外,极少在RTL级编码中使用for循环,这是因为for循环会被综合器展开为所有变量情况的执行语句,每个变量独立占用寄存器资源,不能有效的复用硬件逻辑资源,造成巨大的浪费。一般常用case语句代替。 19. FPGA一般触发器资源比较丰富,而CPLD组合逻辑资源更丰富。 20. FPGA使用的两种语言:VHDL 和 verilog HDL 。 VHDL 为美国国防部发明,用于较多的设计人员合作完成的特大型项目(一百万门以上),语法/结构比较严谨,因为编写出的模块风格清晰。 verilog HDL 第三方支持工具较多,语法结构比VHDL简单,学习来比较容易,仿真工具比较好用,测试激励模块容易编写。 21. 时序设计的实质:电路设计的难点在于时序设计,实质就是满足么一个触发器 建立时间/保持时间 的要求。 (备注:建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间; 保持时间: 触发器在时钟上升沿到来之后,触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。) 22. 为什么触发器要满足建立时间和保持时间? 因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能 稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。 23. 锁存器(latch)和触发器(flip-flop)区别? 电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。 有交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发。可以认为是两个不同电平敏感的锁存器串连而成。前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。 24. and so on. 最后,我们来简单聊一聊FPGA的应用范围。FPAG的应用越来越广泛,航天航空、汽车驾驶、医疗、广播、测量测试、消费电子、工业控制、计算机设备、武器装备等等。从应用场景角度分析,我们可以看到随着谷歌的阿尔法狗打败了人类围棋冠军后,深度学习已经从神坛走下来,越来越多的人开始认识到深度学习可能会改变未来的生活,成为未来科技发展的方向;而FPGA设计工具使其对深度学习领域经常使用的上层软件兼容性更强,FPGA正是助力深度学习的一大技术。不同于CPU的是,FPGA和GPU内都有大量的计算单元,因此它们的计算能力都很强。在进行神经网络运算的时候,两者的速度会比CPU快很多。但是GPU由于架构固定硬件原生支持的指令固定了,而FPGA则是可编程的。 随着国家综合实力越来越强大,国民经济越来越好,FPGA从之前的运用广泛的军工行业在慢慢延伸到民用行业,并且会越来越广泛。 关于FPGA学习的小知识点我们就说到这里,如果大家还想要详细了解,可以留言和楼主一起探讨,欢迎各位留言。 加油,各位!好好学习,天天向上@所有人。 |

举报

举报

举报

举报

举报

举报

举报

举报

举报

举报

更多回帖