完善资料让更多小伙伴认识你,还能领取20积分哦, 立即完善>

3天内不再提示

完善资料让更多小伙伴认识你,还能领取20积分哦, 立即完善>

电子发烧友论坛

电子发烧友论坛|

|

|

相关推荐

11个回答

|

|

|

由于DAC的非线性造成的

|

|

|

|

|

|

功率差多少?

|

|

|

|

|

|

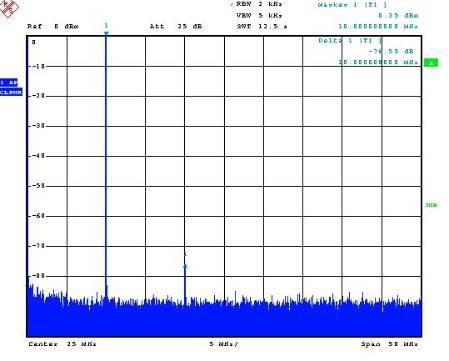

两个功率值差40--50DB,频率越低相差越小。100MHZ以后,二次谐波较小。与ADI给的资料偏差较大。

|

|

|

|

|

|

确实,根据手册上的Figure 9,10MHz下应该有70dB左右的功率差 有没有可能是你使用的电路做了些什么更改,导致不是二次谐波过大而是目标频率被抑制?比如选择了一款低频处截止频率为100MHz左右的变压器? |

|

|

|

|

msvdsufsdf 发表于 2018-11-9 08:18 你好, 这是原理图,PCB,请提意见。原理图上元件按开发板要求设计的。我们今年的用量在1000片以上。 reg0[0]= 0x00; reg0[1]= 0x00; reg0[2]= 0x00; reg0[3]= 0x00;//reg0 // reg1[0]= 0x01; reg1[1]= 0x00; reg1[2]= 0x0c0; reg1[3]= 0x00;//reg1 reg1[0]= 0x01; reg1[1]= 0x00; reg1[2]= 0x00; reg1[3]= 0x080;//reg1 reg2[0]= 0x0d; reg2[1]= 0x07; reg2[2]= 0xc1; reg2[3]= 0x29;//reg2=1000MHZ 25MHZ reg3[0]= 0x00; reg3[1]= 0x00; reg3[2]= 0x7f; reg3[3]= 0x7f;//reg3 reg4[0]= 0xff; reg4[1]= 0xff; reg4[2]= 0xff; reg4[3]= 0xff;//reg4 reg7[0]= 0x4c; reg7[1]= 0xcc; reg7[2]= 0xcc; reg7[3]= 0xcd; //reg7 reg8[0]= 0x00; reg8[1]= 0x00; //reg8 reg9[0]= 0x00; reg9[1]= 0x00; reg9[2]= 0x00; reg9[3]= 0x00;//reg9 reg10[0]=0x00; reg10[1]=0x00; reg10[2]=0x00; reg10[3]=0x00;//reg10 reg11[0]=0x00; reg11[1]=0x00; reg11[2]=0x00; reg11[3]=0x00; reg11[4]=0x00; reg11[5]=0x00; reg11[6]=0x00; reg11[7]=0x00;//reg11 reg12[0]=0x00; reg12[1]=0x00; reg12[2]=0x00; reg12[3]=0x00; reg12[4]=0x00; reg12[5]=0x00; reg12[6]=0x00; reg12[7]=0x00;//reg12 reg13[0]=0x00; reg13[1]=0x00; reg13[2]=0x00; reg13[3]=0x00;//reg13 reg14[0]=0x3f; reg14[1]=0xff; reg14[2]=0x00; reg14[3]=0x00; reg14[4]=0x017; reg14[5]=0x007a; reg14[6]=0x0cc; reg14[7]=0xcd; //reg14/profile0=100MHZ 这是DDS9910的初始化值。 请提建议。 谢 宋 附件

|

|

|

|

|

|

抱歉,无法查看.ddb文件。AD9910的PCB原理图和Gerber文件在这里可以找到,您可以核对:http://www.analog.com/en/digital-to-analog-converters/direct-digital-synthesis-dds/ad9910/products/EVAL-AD9910/eb.html 我们也有示例代码供您参考:http://www.analog.com/zh/content/cast_index_code_example/fca.html |

|

|

|

|

dang28 发表于 2018-11-9 08:50 AD9910二次谐波问题,未解决,这是原理图,我已下载ADI的参考资料,我按资料尝试一下。谢 附件

|

|

|

|

|

|

按下载资料调试软件,无变化,硬件未找出问题,9910在低频时失真严重0.1MHZ---40MHZ,频率越低谐波越大。用示波器看波形时,有失真。频率高(40--300MHZ)时失真小。请ADI提供帮助。 |

|

|

|

|

陈囝囝100 发表于 2018-11-9 09:12 可能与输出的电路设计的关系。AD9910是电流输出,建议负载设置为50欧。所得到的电压值应该限制在voltage compliance range 内。 |

|

|

|

|

dang28 发表于 2018-11-9 09:30 我是按50欧阻抗设计的,registerE 设为幅度最大值,幅度较小时,波形也失真。REGISTER3为中间值。 100KHZ到100MHZ均有高次谐波。未达到标准50--60DBC。 |

|

|

|

|

陈囝囝100 发表于 2018-11-9 09:40 下面是使用AD9910评估板的10MHz的测试结果,评估板后面的滤波器是一个400MHz的宽带滤波器。谐波比较低。建议将您的电路与评估板原理图相比较。

|

|

|

|

|

只有小组成员才能发言,加入小组>>

ADP5092 SYS端口为2.09V,但是REG_OUT为0是什么原因?

1290 浏览 1 评论

ad7193差分输入ain1与ain2差是正值时,读到电压与实际值误差小,但为负值值,误差就变的很大

3917 浏览 2 评论

8574 浏览 1 评论

2914 浏览 1 评论

6703 浏览 2 评论

ADC3442采集,分析数据出现有规则毛刺,请问是哪方面的问题啊?

699浏览 3评论

AD7190状态寄存器一直是0x80,连续转换模式下RDY不拉低

1011浏览 2评论

ad7193差分输入ain1与ain2差是正值时,读到电压与实际值误差小,但为负值值,误差就变的很大

3917浏览 2评论

938浏览 2评论

722浏览 1评论

/6

/6

小黑屋| 手机版| Archiver| 电子发烧友 ( 湘ICP备2023018690号 )

GMT+8, 2024-4-19 00:31 , Processed in 0.559363 second(s), Total 55, Slave 49 queries .

Powered by 电子发烧友网

© 2015 bbs.elecfans.com

关注我们的微信

下载发烧友APP

电子发烧友观察

版权所有 © 湖南华秋数字科技有限公司

电子发烧友 (电路图) 湘公网安备 43011202000918 号 电信与信息服务业务经营许可证:合字B2-20210191

淘帖

淘帖 2207

2207